- 您现在的位置:买卖IC网 > Sheet目录2005 > LTC2224IUK#TRPBF (Linear Technology)IC ADC 12BIT 135MSPS SAMPL 48QFN

LTC2224

10

2224fa

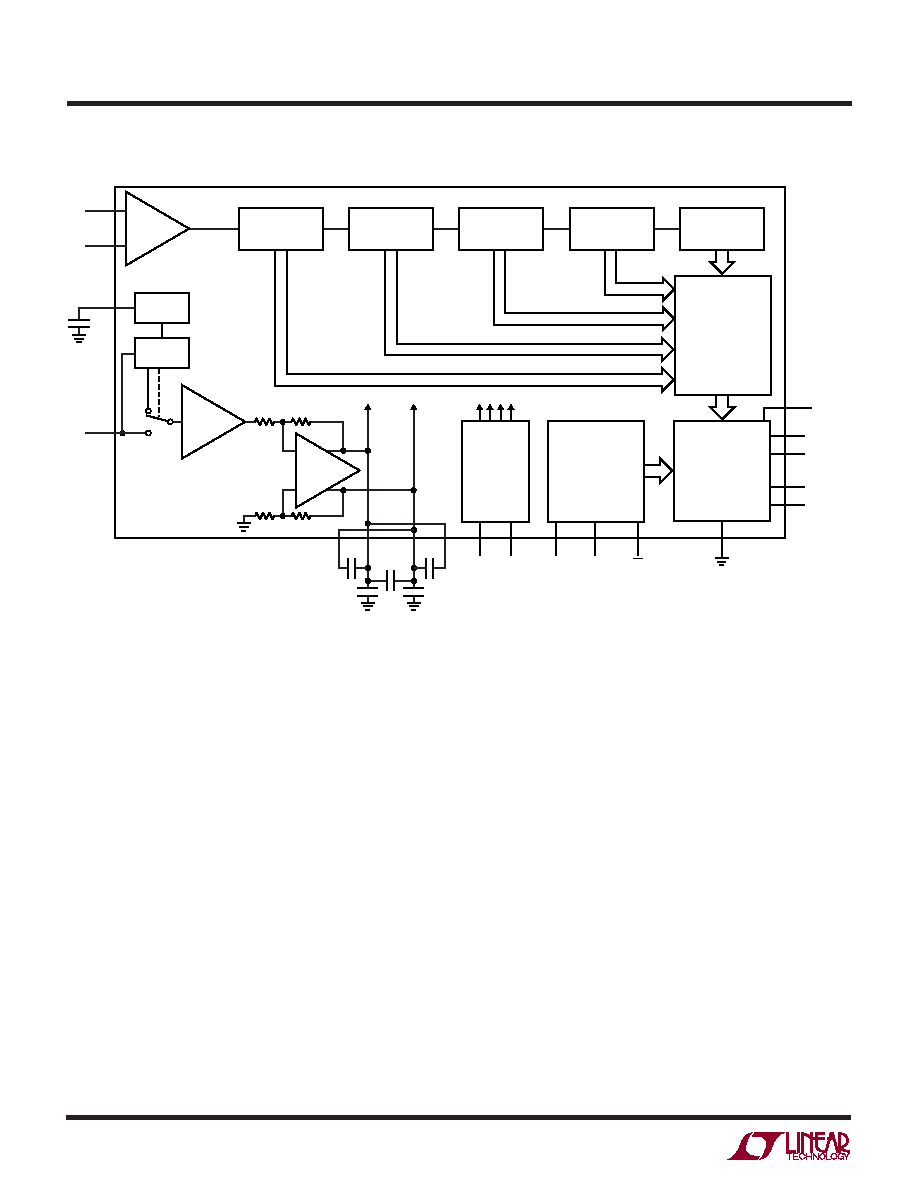

FUNCTIONAL BLOCK DIAGRA

UU

W

Figure 1. Functional Block Diagram

DIFF

REF

AMP

REF

BUF

2.2

F

1

F

0.1

F

0.1

F

1

F

INTERNAL CLOCK SIGNALS

REFH

REFL

DIFFERENTIAL

INPUT

LOW JITTER

CLOCK

DRIVER

RANGE

SELECT

1.6V

REFERENCE

ENC+

REFHA

REFLB

REFLA REFHB

ENC–

SHIFT REGISTER

AND CORRECTION

OE

M0DE

OGND

OVDD

2224 F01

INPUT

S/H

SENSE

VCM

AIN

–

AIN

+

2.2

F

FIRST PIPELINED

ADC STAGE

FIFTH PIPELINED

ADC STAGE

FOURTH PIPELINED

ADC STAGE

SECOND PIPELINED

ADC STAGE

THIRD PIPELINED

ADC STAGE

OUTPUT

DRIVERS

CONTROL

LOGIC

SHDN

OF

D11

D0

CLOCKOUT

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC2225IUH#TRPBF

IC ADC 12BIT 10MSPS 3V 32-QFN

LTC2228IUH#TRPBF

IC ADC 12BIT 65MSPS SAMPL 32-QFN

LTC2229IUH#PBF

IC ADC 12-BIT 80MSPS 3V 32-QFN

LTC2231IUP#TRPBF

IC ADC 10BIT 135MSPS 64-QFN

LTC2233CUK#TRPBF

IC ADC 10BIT 80MSPS SAMPL 48QFN

LTC2234IUK#TRPBF

IC ADC 10BIT 135MSPS SAMPL 48QFN

LTC2237IUH#TRPBF

IC ADC 10BIT 40MSPS 3V 32-QFN

LTC2239CUH#PBF

IC ADC 10-BIT 80MSPS 3V 32-QFN

相关代理商/技术参数

LTC2224UK

制造商:LINER 制造商全称:Linear Technology 功能描述:12-Bit, 135Msps ADC

LTC2225

制造商:LINER 制造商全称:Linear Technology 功能描述:14-Bit, 80Msps Low Power 3V ADC

LTC2225CUH

制造商:Linear Technology 功能描述:ADC Single Pipelined 10Msps 12-bit Parallel 32-Pin QFN EP

LTC2225CUH#PBF

功能描述:IC ADC 12-BIT 10MSPS 3V 32-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6

LTC2225CUH#TR

制造商:Linear Technology 功能描述:ADC Single Pipelined 10Msps 12-bit Parallel 32-Pin QFN EP T/R

LTC2225CUH#TRPBF

功能描述:IC ADC 12BIT 10MSPS 3V 32-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极

LTC2225IUH

制造商:Linear Technology 功能描述:ADC Single Pipelined 10Msps 12-bit Parallel 32-Pin QFN EP

LTC2225IUH#PBF

功能描述:IC ADC 12-BIT 10MSPS 3V 32-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6